The big, elegant VHDL tutorial just began

Hello everybody! I’ve been using VHDL extensively for around 7-8 months now, as part of the work on my B.Sc thesis, so I thought it would be nice to share with you some of the basics of hardware modeling and verification/testing using VHDL, along with some guidelines and insights for writing easy-to-maintain and readable code.

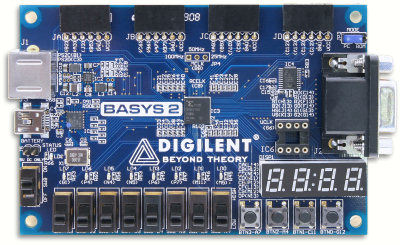

The focus of this series of tutorials will be on design techniques and simulation, using as much open-source tools as possible. So you don’t need to actually implement the tutorials on an FPGA board, although it’s much more fun to do so :) If you want to go beyond simulation and watch actual blinking LEDs, I recommend the BASYS2 board from Digilent. It costs only $49 for students, has nice features and is really one of the most affordable out there. It has a Xilinx FPGA (Spartan3 Family), so you can use the ISE Webpack tools, which installs nicely on Linux and is free-to-use (freeware). More details on installing and using ISE will come later…

Most importantly, how will this tutorial work? It will be a series of posts, and I will do my best to introduce increasingly complex concepts of VHDL and hardware design by using examples, and we will learn good coding practices and methodology from the start. Each post will lead you to write a design, and in the process of writing and testing it you will learn a new concept.

Enough for theory, let’s start today by installing the tools we need: GHDL and GTKWave. These tools will allow you to, respectively, simulate and test your hardware designs and “surf” (view) the waveforms of your simulations.

Installation of both these packages in Ubuntu Linux is (as always) a breeze. Just type the following in a terminal:

sudo aptitude install ghdl gtkwaveOf course there are GHDL and GTKWave packages for other Linux distributions, and also for Windows and Mac OS X. For installation instructions you can visit the download pages for GHDL and GTKWave. After installation, you can open this waveform file in GTKWave just to see it at work: Doubly-Linked list waveform file

in the next post we will implement our first design, a simple 1-bit adder. We will get started with the basic process of modelling, writing, simulating and refactoring VHDL designs. But for now, that’s all folks! :)