Meu TCC

UPDATE (2011-08-01): Há bastante tempo já apresentei e finalizei o trabalho. O relatório está aqui para todo mundo ver :)

Já faz um tempo que iniciei meu último ano no curso de Bacharelado em Ciência da Computação da Universidade Federal de Santa Catarina… E como todo aluno que quer pegar seu diploma, eu devo realizar e apresentar à uma banca avaliadora um Trabalho de Conclusão de Curso, o famoso TCC :)

Mudei muito, mas muito mesmo de idéia sobre o tema de meu trabalho durante todo o curso, mas enfim o defini em setembro de 2010. Estou fazendo meu trabalho final na área de sistemas embarcados e integração software/hardware, no LISHA/UFSC. Vou tentar explicar mais detalhadamente o que vou (tentar) fazer:

Uma questão pela qual me interesso muito desde a 2a. fase (quando descobri os FPGAs e as HDLs) é a implementação de algoritmos e sistemas computacionais diretamente em hardware, sem usar software rodando num microprocessador. De fato, já na 4a. fase (em Teoria da Computação) eu aprendi que o modelo teórico de circuitos booleanos tem a mesma expressividade que a máquina de Turing. O que isso quer dizer, “trocado em bala”, é que todo e qualquer algoritmo que roda em software numa CPU pode ser também implementado usando-se uma rede de portas lógicas.

E há muitos motivos para isso. Muitos algoritmos têm um bom nível de paralelismo, e podem se beneficiar muito de uma implementação em hardware (inerentemente paralelo). Por exemplo, algoritmos de álgebra linear (computação gráfica), reconhecimento de padrões, ordenação e busca. Então um dos “possíveis” temas para meu TCC sempre foi trabalhar com a descrição de algoritmos em hardware, ou como melhorar a maneira com a qual essa descrição é feita, torná-la mais simples e integrada aos softwares convencionais.

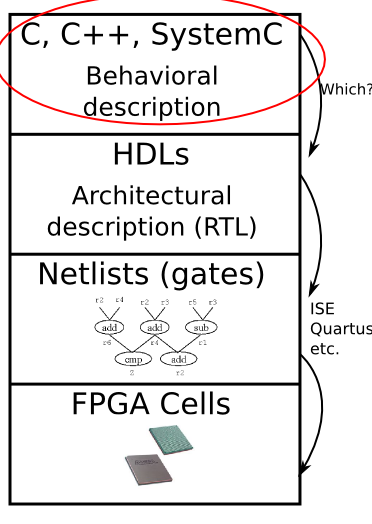

Basicamente, nos dias de hoje, se descreve algoritmos que vão rodar em hardware de uma maneira ainda um tanto primitiva. Os softwares que sintetizam modelos em HDL para FPGAs trabalham com uma descrição arquitetural do circuito. Isso quer dizer que você escreve seu algoritmo em termos de blocos funcionais e como eles se conectam. Você deve especificar todos os detalhes de interconexão entre esses blocos (quais fios se conectam em quais) e também especificar manualmente os protocolos de comunicação entre blocos. Na maioria dos casos, porém, essas tarefas poderiam ser realizadas automaticamente por uma ferramenta, e nós programaríamos somente a parte que importa, o “comportamento” do algoritmo.

E aí que entra o tema do meu TCC. Já existem algumas ferramentas que prometem automatizar todo esse processo de detalhamento de um circuito, e eu pretendo descrever um circuito complexo usando-as e comparar tal descrição automática à descrição de baixo-nível (RTL) feita manualmente. O circuito que pretendo descrever será um escalonador para o sistema operacional EPOS. Enquanto a maior parte do SO rodará em uma CPU convencional, o escalonador estará implementado em hardware. Portanto, também faz parte do meu TCC o estabelecimento e uso de uma interface para a comunicação entre componentes implementados em hardware e software.

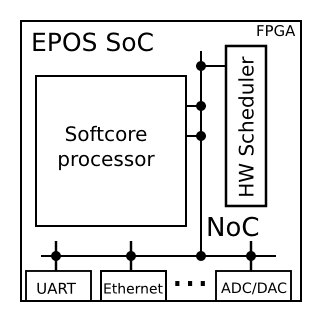

Bem, sem muita enrolação, aí vai uma figura de como deve ficar o sistema todo :)

A NoC mencionada na figura é uma rede-no-chip (Network-on-Chip), e é o termo técnico que se usa para referir à uma malha de interconexão dentro da FPGA. Além do meu humilde escalonador :) outros componentes também estarão conectados (como interface serial, rede Ethernet), para permitir que o sistema possa ser testado.

Bem, é isso aí. Atualmente estou trabalhando na interface entre o processador que escolhemos pra trabalhar (Plasma softcore) e a memória. Essa mesma interface (AMBA) também vai ser provavelmente usada para a comunicação entre CPU e escalonador. Meu próximo passo então vai ser fazer a descrição do escalonador em si, usando C++ com a ajuda da ferramenta Catapult-C.

Vamos ver se tudo dá certo, se der mais ou menos certo já me vale um bacharelado… :)